CPU Design using LogiSim

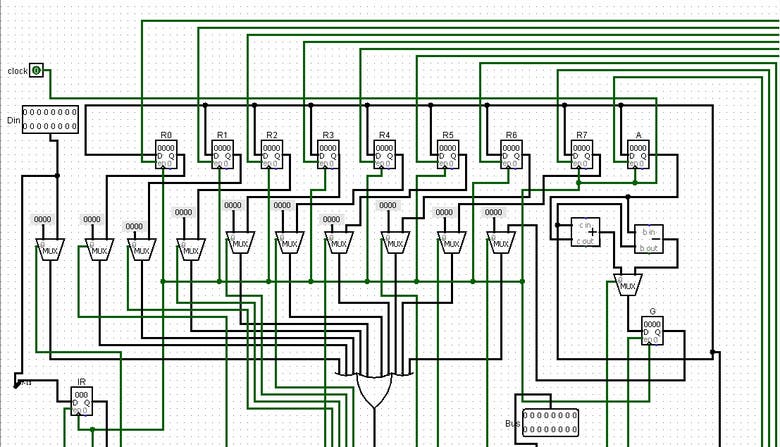

Figure 1 shows a digital system that contains a number of 16-bit registers, a multiplexer, an adder/subtracter unit, a counter, and a control unit. Data is input to this system via the 16-bit DIN input. This data can be loaded through the 16-bit wide multiplexer into the various registers, such as R0, . . . , R7 and A. The multiplexer also allows data to be transferred from one register to another. The multiplexers output wires are called a bus in the figure because this term is often used for wiring that allows data to be transferred from one location in a system to another. Addition or subtraction is performed by using the multiplexer to first place one 16-bit number onto the bus wires and loading this number into register A. Once this is done, a second 16-bit number is placed onto the bus, the adder/subtracter unit performs the required operation, and the result is loaded into register G. The data in G can then be transferred to one of the other registers as required. \\n

Mi perfil

A FPGA/IC design expert with 7+ years experience and hundreds of FPGA/Verilog/VHDL projects using Xilinx/Altera FPGA Design Tools and Digital Logic Design using LogiSim/CEDAR. Founder of FPGA4student. Expertise: FPGA, Verilog, VHDL, Xilinx ISE, Vivado, Altera Quartus, Modelsim, Logisim, CEDAR, MIPS Assembly, PLP Tools, Qtspim, MARS, PCB Design, Altium Designer, OrCAD, PSpice, Proteus, Arduino, CMOS VLSI Design, Cadence Virtuoso, Layout XL, Digital IC Design from RTL to GDSII, Analog IC Design. - Featured FPGA projects: + Video/Image Processing on FPGA: FPGA/Verilog/VHDL Implementation of Gesture Recognition, Fingerprint Identification, Image Compression in Wavelet Domain using DWT and SPIHT, Image Enhancements including Noise Filtering. + Fixed-point and Floating Point FPGA projects in Verilog/VHDL + AES, SHA 128, 192, 256 Implementations on FPGA + Single/Multicycle/Pipelined RISC/MIPS Processors in Verilog/VHDL/Logisim + Games on FPGA and many other FPGA projects